### Juillet - Août 2005 - N°21

# **Photolithographie**

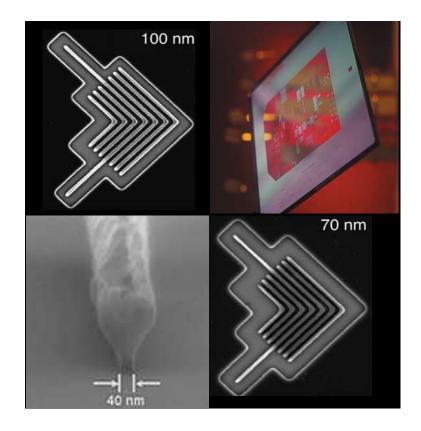

L'industrie des semiconducteurs a connu ces dernières années un de ses plus forts taux de croissance (+27% en 2004), après la chute des ventes occasionnée par l'éclatement de la bulle internet en 2001. Si les profits et la demande augmentent, le coût de réalisation des composants suit la même tendance. Avec le temps, la complexité des composants s'accroît et les étapes de réalisation se multiplient en appliquant un même modèle de fabrication : dépôt, photolithographie, gravure, dopage,... Le nombre de niveaux d'interconnexions atteint aujourd'hui la dizaine de couches, chacune nécessitant la reproduction des mêmes procédés. Dans ce contexte, les techniques de photolithographie (définition des zones actives du circuit) sont cruciales mais coûteuses et contribuent en majeure partie à la prosperité de l'industrie des semiconducteurs. En 2007, la génération 65 nm succèdera à la génération 90 nm débutée en 2004, où la longueur des grilles atteindra 35 nm avec un contrôle sur les dimensions de 2,2 nm (Source : ITRS). Alors que l'industrie photolithographique a réussi jusqu'à présent à relever les défis technologiques se trouvant sur son chemin, les limites physiques et les coûts exorbitants des procédés font douter de la faisabilité des nouveaux objectifs définis par l'ITRS. Aujourd'hui les nanotechnologies sont activement développées pour prendre le relais des techniques de photolithographie optique, l'industrie se trouvant confrontée à un changement obligatoire à moyen terme de son infrastructure. Quels seront les successeurs des techniques de photolithographie optique? Les objectifs de la *roadmap* sont-ils réalisables dans les temps? Quels sont les efforts de recherche américains dans ce domaine?

### Editorial

#### Introduction

- A Economie de la photolithographie

- 1) Industrie des semiconducteurs

- 2) Industrie photolithographique

- Etat du marché

- Retours sur Investissements difficiles

- 3) Les grands acteurs indutriels

- 4) Les investissements R&D

- 5) Les grands pôles technologiques américains

- Texas

- New-York

- Autres initiatives de recherche

- B Technologie

- 1) Principe

- 2) Les procédés de la NGL

- a) Lithographie 193 nm par immersion

- b) Lithographie 157 nm

- c) Extrême UV

- d) Nanoimprint

- e) Dip Pen Nanolithography

- f) Lithographie sans masque

- g) Techniques d'auto-assemblage

#### Conclusion

## **Editorial**

# Enjeu photolithographique

Les techniques lithographiques sont au cœur de l'industrie électronique, et les progrès réalisés dans ce domaine ont, depuis plusieurs décennies, permis la course à la miniaturisation des composants. A la lecture de ce nouveau dossier, vous pourrez constater que les grandes thématiques que nous abordons sur le thème de la lithographie sont facilement généralisables à l'ensemble des industries de haute technologie :

- Une course entre les grandes entreprises et les grandes nations industrialisées pour la mise au point de nouveaux procédés dans un contexte de concurrence exacerbée pour s'accaparer les marchés en croissance, en particulier les marchés asiatiques.

- Une mobilisation aux Etats-Unis réunissant tous les acteurs du développement technologique et économique : pouvoirs publics au niveau fédéral (agences de recherche des différents ministères) comme au niveau des différents états, chercheurs et laboratoires académiques, centres de transfert de technologies, capitaux risqueurs et entreprises. Dans certaines zones géographiques, l'environnement particulièrement propice à la création d'activités attire naturellement les entreprises de technologie, qu'il s'agisse de grands groupes (Intel, IBM...) ou de start-ups.

- L'apparition de nouveaux pôles de compétitivité (clusters technologiques) qui émergent à travers les Etats-Unis, en particulier dans le secteur de la lithographie dans les états de New York et du Texas, et qui se positionnent en concurrence de la Silicon Vallée.

- Un développement des nanotechnologies qui sont attendues comme des technologies de rupture constituant une réelle alternative au développement et à l'amélioration des techniques désormais traditionnelles de la photolithographie. Ces nanotechnologies donnent déjà lieu à de la création d'entreprises et d'activités économiques.

Ce dossier montre que les entreprises et les laboratoires américains restent à la pointe de la recherche en matière d'électronique et en particulier de lithographie. Au-delà des considérations technologiques, deux sujets ont récemment agité le secteur : l'annonce par Apple de s'équiper désormais en microprocesseurs Intel au détriment des puces IBM et enfin plus récemment la plainte d'AMD contre Intel auprès des autorités de concurrence : preuve que la lutte entre les géants de l'électronique ne se limite pas à une course technologique... Nous continuerons bien entendu à suivre ces différents développements.

Christophe Lerouge Attaché pour la Science et la Technologie San Francisco

## Introduction à la photolithographie

Quand Intel a présenté au public en 1986 sa première puce type 386, son coût de développement était de 15 Millions de \$ (M\$) [1]. Aujourd'hui, ces coûts pour réaliser une dernière génération de composants sont passés à 16 Milliards de \$ (G\$) à cause de la complexité des procédés ajoutée à la multiplication des étapes de réalisation. C'est en même temps grâce à cette complexité toujours plus grande que les performances des composants se sont accrues. Les évolutions projetées suivant la loi de Moore<sup>1</sup>, énoncée en 1965, ont été respectées et ont permis l'avènement des technologies numériques et la démocratisation des appareils électroniques présents aujourd'hui dans la majorité des foyers.

Alors que la vitesse du traitement de l'information augmentait initialement de 17% par an, ce rythme s'est nettement ralenti depuis une dizaine d'années à cause des difficultés techniques rencontrées à chaque nouvelle génération de composants. Pour contrer ces écueils, l'industrie des semiconducteurs a été obligée de se regrouper en consortium (ITRS, Sematech, EUV LLC, ...) afin de concentrer les énergies sur des problèmes techniques récurrents. L'évidence de ce ralentissement et de la difficulté de trouver des innovations technologiques apparaît également dans les solutions intermédiaires que les industriels sont obligés d'utiliser quand aucune autre alternative manufacturable n'existe. La version 2003 de l'ITRS [2] a ainsi introduit dans ses cases une mention spéciale "solutions intérimaires" pour caractériser ces solutions. Le silicium contraint en tension en est un bon exemple, où pour augmenter le courant de saturation des transistors, le canal de conduction est réalisé par une couche de silicium contraint ceci afin d'augmenter la mobilité des électrons. Des innovations majeures devront ainsi rapidement voir le jour pour conserver le modèle actuel de croissance : des nouveaux matériaux pour les diélectriques de grille (matériaux high-k), des électrodes de grille métalliques, de nouveaux diélectriques pour isoler les interconnexions,...

Parmi tous les procédés nécessaires à la réalisation des composants semiconducteurs, la photolithographie est une étape clé sur laquelle repose en majeure partie l'avenir de l'industrie. Le procédé représente à lui seul au moins un tiers du prix total des composants. Sematech Inc. (Austin, TX), une association à but non lucratif ayant pour objectif d'améliorer la collaboration des grands acteurs du domaine des semiconducteurs, a publié fin avril [3] une liste des grands challenges que l'industrie microélectronique devra relever dans les années à venir. Beaucoup de ces problèmes concernent le domaine photolithographique :

- amélioration des optiques et des revêtements pour la

lithographie par immersion;

- infrastructure des masques (193 nm et Extrême UV);

- nouveaux types de résines amplifiées chimiquement;

- infrastructure EUV (masques sans défauts, durabilité des optiques, sensibilité des résines).

Si les techniques de photolithographie optique devraient permettre de réaliser la prochaine génération de composants (65 nm en 2007), il est fondamental de prévoir les limites à venir et renouveler l'infrastructure lithographique à temps. L'industrie microélectronique est à l'aube d'une **Nouvelle Génération Lithographique (NGL)** qui décidera de son évolution, loi de Moore ou pas.

# Economie de la photolithographie

### 1) Industrie des semiconducteurs :

L'industrie des semiconducteurs a connu une phase de forte croissance (+23,4%) en 2004 avec un total des ventes mondiales estimé à 219,9 G\$ (Gartner Inc.). Pour 2005, les prévisions sur les ventes¹ sont de +6,3% selon la Semiconductor Industry Association (SIA). Ces chiffres relativement faibles s'expliquent par la fin d'un cycle de croissance entamé après l'éclatement de la bulle internet en 2001. Une baisse des prix des mémoires DRAM et Flash est également à noter pour expliquer ce phénomène : la vente des mémoires DRAM a baissé de 7 % en Avril par rapport à Mars (SIA). Or le marché des mémoires représente un bon indicateur du dynamisme du secteur des semiconducteurs dans son intégralité : une baisse du marché des DRAM entraînera une baisse du marché global et inversement.

Les facteurs de la croissance du secteur [1] sont dominés par :

- le marché de l'électronique grand public : depuis quelques années, la vente de téléviseurs numériques est en plein boom (+65 % en 2005), de même pour les appareils photos numériques (+13% pour 2005).

- le marché des télécommunications : l'ajout de fonctionnalités aux téléphones mobiles a augmenté de 25 % la quantité de composants semiconducteurs présents dans les téléphones. Ce secteur a par ailleurs cru d'environ 30 % en 2004.

- le marché des PC : de nouvelles fonctions *streaming* et haut débit rendent ce marché toujours performant avec une croissance de 10 % en 2004.

<sup>&</sup>lt;sup>1</sup> La loi de Moore prévoit un doublement de la densité d'intégration des transistors sur une puce tous les 18 mois.

<sup>&</sup>lt;sup>1</sup> Ces chiffres sont issus de bulletins prévisionnels délivrés par la Semiconductor Industry Association avec le World Semiconductor Trade Statistic (WSTS), organisme à but non lucratif publiant des données statistiques sur le marché des semiconducteurs.

Au niveau géographique (Tableau 1), si l'Amérique du Nord et l'Europe enregistrent des ventes faibles, la zone Asie-Pacifique s'impose comme un marché fort et dynamique (+11,3%) dans un contexte terne. Le montant des ventes de semiconducteurs a ainsi été évalué à 102,4 G\$ en 2004 et devrait atteindre 166 G\$ en 2010 dans cette zone. Le Japon réagit le plus mal à la baisse des ventes de DRAM et enregistre ses plus faibles ventes de semiconducteurs depuis août 2003.

| Secteur géographique | Avril 2005/2004 |

|----------------------|-----------------|

| Amérique             | +3,9 %          |

| Europe               | +4,6%           |

| Japon                | -6%             |

| Asie-Pacifique       | +11,3%          |

Tableau 1 : Total des ventes de semiconducteurs au mois d'Avril 2005 par rapport à Avril 2004, suivant les quatre grandes zones géographiques mondiales. Source SIA

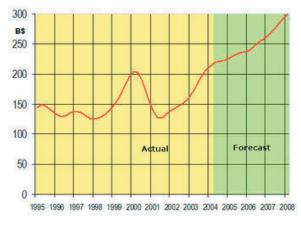

L'année 2006 devrait marquer le retour d'une croissance plus forte du marché (Fig.1), + 9,8% de croissance annuelle moyenne jusqu'en 2008 selon WSTS, pour passer la barre des 300 G\$ en 2008.

Fig. 1 : Evolution et prévision des ventes de semiconducteurs de 1995 à 2008 (G\$). Source : WSTS

# 2) Industrie photolithographique:

#### a) Etat du marché:

L'industrie des semiconducteurs et de l'équipement pour semiconducteurs a connu une forte croissance depuis ses débuts. De 1972 jusqu'au milieu des années 90, l'industrie a bénéficié d'une croissance annuelle moyenne de 15 à 17 %. Ce chiffre est toutefois moins important aujourd'hui avec des revenus annuels en hausse de 10 à 12 %. Dans le même temps, les demandes ont augmenté jusqu'à atteindre des niveaux historiques.

Compris dans le secteur global de l'équipement pour semiconducteurs, le marché de la photolithographie est en très

forte croissance depuis 2004 (+58% selon Information Networks et +68% selon Semi Inc.).

Il est estimé cette année à 4,8 G\$ (WSTS). A contrario, le secteur global de l'équipement pour semiconducteurs est entré dans une phase de baisse (Tableau 2) : -12,2% en 2004 par rapport à 2003 avec un total des ventes à 24,8 G\$. Les analystes prévoient néanmoins que des investissements stratégiques par les acteurs majeurs du secteur devraient niveler cette baisse en 2005. Les estimations des ventes en 2007 atteignent 6,4 G\$, chiffres excédant pour la première fois les 6 G\$ obtenus en 2000.

| Année                    | 2003  | 2004  | 2005  | 2006  | 2007  | 2008  |

|--------------------------|-------|-------|-------|-------|-------|-------|

| Montant des ventes (G\$) | 28,22 | 24,78 | 23,71 | 26,88 | 36,51 | 30,02 |

| Croissance               | 68,6  | -12,2 | -4,3  | 13,4  | 35,8  | -17,8 |

Tableau 2 : Prévisions des ventes d'équipements pour semiconducteurs de 2003 à 2008 pour les procédés de front-end : préparation, dépôt, photolithographie, gravure, stripping, implantation. Source Semi Inc.

Cette baisse des revenus actuels malgré une augmentation de la demande provient d'une part, de la baisse des prix des semiconducteurs, mais aussi d'un regain de compétition entre les fabricants, le déplacement des usines de production en Asie (développement des usines fabless) alliés au ralentissement des cycles technologiques [4].

Au niveau géographique (Tableau 3), le Japon (23%) et Taïwan (21%) représentent les marchés les plus importants pour l'équipement des semiconducteurs, devant les Etats-Unis (17%).

| Région              | Revenus<br>2003 (G\$) | Revenus<br>2004 (G\$) | Croissance % |

|---------------------|-----------------------|-----------------------|--------------|

| Japon               | 5.56                  | 8.28                  | 49%          |

| Taïwan              | 2.90                  | 7.76                  | 168%         |

| Amérique du<br>Nord | 4.73                  | 5.81                  | 23%          |

| Corée               | 3.18                  | 4.61                  | 45%          |

| Europe              | 2.56                  | 3.44                  | 34%          |

| Chine               | 1.15                  | 2.68                  | 133%         |

| Reste du monde      | 2.10                  | 4.49                  | 114%         |

| Total               | 22.18                 | 37.08                 | 67%          |

Tableau 3 : Ventes d'équipements pour semiconducteurs en 2004 suivant les pays et zones géographiques mondiales. Source Semi Inc.

### b) Retours sur Investissement (ROI) difficiles :

Le rythme d'introduction régulier de nouvelles générations technologiques joue un rôle important dans la difficulté des entreprises à accroître leur marge de profit. Depuis l'édition 2003 de l'ITRS, la durée des cycles technologiques est remontée à trois ans, notamment à cause de challenges grandissants : introduction d'une nouvelle génération lithographique, remplacement des diélectriques de grille, consommation excessive des composants,... Ajouté à cela, les fondeurs font également face à deux tâches majeures: acquérir de nouvelles lignes de production basées sur les technologies les plus récentes pour les dernières générations de composants et continuer à faire fonctionner et maintenir les appareils de production des générations antérieures. Aujourd'hui, les industriels travaillent au développement de la génération 45 nm (2010), les premiers pilotes apparaissent pour le 65 nm et les technologies 90 nm, 130 nm et 180 nm sont couramment utilisées pour la production de masse. Ceci totalise cinq lignes de production à développer ou maintenir affectant la rentabilité des entreprises. Ainsi les coûts de fabrication et de maintenance se montent à plusieurs milliards de \$ par an et les dépenses à venir vont être encore plus importantes. Pour le design des composants, les coûts sont multipliés par trois chaque année et par deux pour les masques photolithographiques. L'industrie va devoir créer un équilibre entre les coûts de développement d'une technologie (Cost of Ownership : CO) et les bénéfices perçus par la diminution de la taille des composants pour assurer leur ROI.

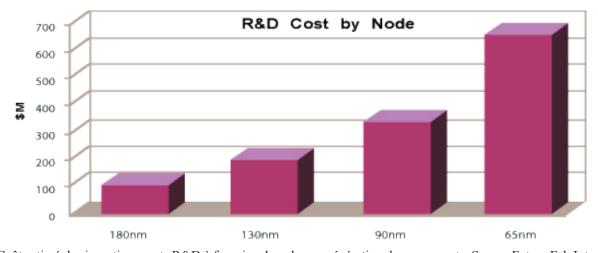

Le coût de la technologie 65 nm va augmenter de manière importante par rapport aux autres générations (Fig.2) avec notamment des scanners 193 nm coûtant plus de 15 M\$ l'unité (les scanners à la fin des années 80 coûtaient 1 M\$). Selon le géant du manufacturing taïwanais TSMC, le passage de la technologie 90 à 65 nm devrait être également techniquement plus difficile que les générations antérieures. Le prix d'un jeu de masques pour la génération 65 nm excèdera le million de \$ et des augmentations de 20 à 30 % sont encore attendues pour

les prochaines générations (Montgomery Research Inc.). Les motifs de corrections optiques (Optical Proximity Correction) sont devenus nécessaires à l'amélioration de l'image du masque dans la résine et compliquent les procédés de production. Même constat pour les résines qui vont nécessiter des améliorations majeures : aujourd'hui les longueurs de diffusion des résines à amplification chimique approchent les dimensions des transistors. Au total, le coût d'introduction d'une technologie photolithographique en production est estimée à 1 G\$ (Montgomery Research Inc.).

Sur les dix dernières années, l'industrie a souffert d'un manque global de profit, autant pour les fondeurs que les équipementiers. Les résultats financiers publiés par 32 équipementiers [4] ont montré que l'industrie a subi un léger déficit annuel de 1,8%. Alors que le nombre d'appareils lithographiques vendus devrait chuter de 7 % en 2005, les revenus vont rester stables grâce à l'augmentation du prix de vente des steppers à 193 nm par immersion. Actuellement, la compagnie hollandaise ASML domine le marché avec 39% des ventes et 50% des revenus, mais l'introduction des techniques lithographiques à 193 nm par immersion devrait modifier les parts de marché de chaque constructeur (ASML, Nikon et Canon).

## 3) Les grands acteurs industriels

ASML, Canon et Nikon se partagent le marché des appareils de production lithographiques. ASML, basé aux Pays-Bas, est le leader mondial des appareils d'exposition photolithographiques, ou stepper. Il développe des techniques de lithographie sèche, par immersion et Extrême UV. ASML et IBM ont annoncé en janvier dernier la création d'un centre de R&D en nanoélectronique installé à Albany dans l'état de NY. Ce centre baptisé "International Multiphase Partnership for Lithography Science and Engineering (IMPLSE)" est le premier centre à l'étranger de ASML, qui vient d'y installer en début d'année un de ses premiers appareils de lithographie

Fig.2 : Coût estimé des investissements R&D à fournir selon chaque génération de composants. Source Future Fab International

par immersion. Le montant total de l'investissement de l'Etat et des industries atteint les 400 M\$ sur 5 ans avec une cinquantaine d'entreprises new-yorkaises implantées sur le site [5]. Egalement présents à Albany, Sematech North, Tokyo Electron et IBM font de la région un pôle majeur en nanoélectronique (Voir chapitre - Les grands pôles de recherche aux USA). En Europe, l'IMEC (Belgique) fait partie des centres pionniers sur la recherche en nanoélectronique et pour l'introduction de la lithographie par immersion en 2007 en production. L'IMEC collabore également avec ASML sur l'EUV et a prévu d'installer un appareil d'exposition plein champ fin 2005 dans le cadre du programme "IMEC Industrial Affiliation Program on EUV Lithography" [6]. De nombreuses entreprises participent à ce programme : Infineon Technologies, Intel, Matsushita, Philips, Samsung et Texas Instruments. Au niveau des équipementiers, Applied Materials Inc., basé à Santa Clara (CA), a annoncé récemment sa décision de créer une holding de sa compagnie en Chine [7] soulignant la position stratégique de la Chine dans la production de semiconducteurs et la nécessité de se positionner sur ce marché. En effet, selon Semi Inc., une vingtaine de nouvelles usines de production devraient voir le jour en Chine entre 2005 et 2008 en raison d'une consommation locale de circuits intégrés de plus en plus importante [8].

## 4) Les investissements R&D

Le premier trimestre 2005 a montré un investissement massif en R&D de la part des grands acteurs du secteur microélectronique (Tableau 4). Le fondeur taïwanais TSMC a ainsi dépensé presque la moitié de son budget annuel au cours du premier quart 2005 et prévoit des investissements en demiteintes pour la fin de l'année (baisse possible de 32% selon IC Insights).

| Capitaux Investis (1Trimestre05) / Budget Total 2005 |                        |                            |                                         |

|------------------------------------------------------|------------------------|----------------------------|-----------------------------------------|

| Société                                              | Dépenses<br>1T05 (M\$) | Budget total<br>2005 (M\$) | % du budget<br>total investi<br>au 1T05 |

| TSMC                                                 | 1.210                  | 2.600                      | 47%                                     |

| ST                                                   | 564                    | 1.600                      | 38%                                     |

| AMD                                                  | 518                    | 1.600                      | 36%                                     |

| SMIC                                                 | 343                    | 1.000                      | 34%                                     |

| Infineon                                             | 505                    | 1.500                      | 34%                                     |

| Intel                                                | 1.788                  | 5.800                      | 32%                                     |

| Samsung                                              | 1.720                  | 5.725                      | 30%                                     |

Tableau 4 : Classement des entreprises suivant leurs investissements R&D au premier trimestre 2005. Source : IC Insights

Globalement, les capitaux investis par les industriels restent faibles même si les prévisions sur les ventes sont à la hausse.

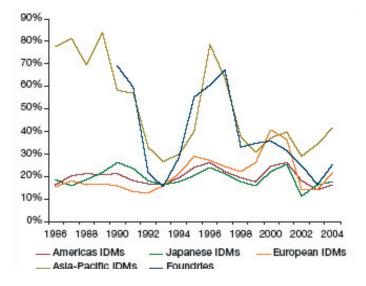

Les dépenses en moyenne devraient baisser de 5 % par rapport à l'année dernière avec un total à 43,4 G\$. Au niveau des capitaux investis et des revenus perçus (Fig.3), les Etats-Unis ont eu les dépenses totales les plus fortes sur les 20 dernières années, mais les compagnies de la zone Asie-Pacifique ont eu un Retour sur Investissement (ROI) plus élevé.

Fig. 3 : Evolution des capitaux investis suivant les grandes zones géographiques mondiales. Source : Montgomery Research Inc.

Les niveaux d'investissements dans le secteur des semiconducteurs et de l'électronique de la part des capitaux risqueurs se portent bien avec une levée de fonds de 1101,2 G\$ dans la première moitié 2005, moins bien toutefois que les résultats 2004 (1285,4 G\$).

### 5) Les grands pôles technologiques américains

Alors que la Silicon Valley continue de dominer technologiquement et économiquement les clusters technologiques aux Etats-Unis, les états du Texas et de New-York présentent un fort dynamisme au niveau de la recherche en nanotechnologies.

<u>Texas</u>: Depuis la création de Sematech à Austin en 1986, le Texas est considéré comme un pôle de recherche international dans le secteur des semiconducteurs. Austin, lieu d'implantation d'un cluster de haute technologie au Texas, accueille de grandes institutions de recherche industrielle (Sematech, Applied, Texas Instruments) et de prestigieuses universités: Universités du Texas, Rice,...

<sup>&</sup>lt;sup>1</sup> Ces chiffres sont issus du Venture Capital Counter tenu par Silicon Strategies.

Le gouverneur actuel du Texas Rick Perry, cherche à relancer l'économie de l'Etat en misant sur un investissement massif dans les entreprises de haute technologie comme Molecular Imprint Inc. (MII)<sup>1</sup>, pionniers des techniques de nanoimprint. Ce plan stratégique, la Texas Technology Initiative [9], vise à générer 3 G\$ de bénéfices pour les industries de pointe dans les dix ans à venir, qui en retour partageront leurs ressources avec l'état. L'Emerging Technology Fund [10] rentre dans le cadre de cette initiative stratégique afin de créer des emplois hautement qualifiés pour le Texas. Ce fond est estimé à 300 M\$ et a pour but de promouvoir les partenariats de recherche entre les universités et les entreprises privées : l'Université du Texas à Austin collabore ainsi avec Sematech autour d'une joint venture, le Advanced Materials Research Center [11], qui a reçu 40 M\$ de la part de l'état l'année dernière. Ce centre se focalise particulièrement sur les techniques de photolithographie : immersion, EUV, lithographie sans masque, auto-assemblage. Déjà plusieurs entreprises comme Applied Materials Inc., le plus gros fournisseur d'équipements pour semiconducteurs, a annoncé la décision d'établir des programmes de recherche au Texas si elle obtient les subventions de l'Etat.

Le Texas abrite également l'alliance SPRING "Strategic Partnership for Research in Nanotechnology", un partenariat d'universités visant à améliorer les collaborations et la promotion des nanotechnologies [12]. Le projet regroupe six universités texanes : Université du Texas à Austin (UT Austin), UT Dallas, UT Arlington, UT Pan American, UT Brownsville et l'Université de Rice. L'United States Air Force Research Laboratory basé à Dayton (Ohio) soutient financièrement une partie des projets menés par SPRING.

New York: Lors du discours 2005 sur le "State of the State Adress" [13], le gouverneur de l'état de New-York Georges Pataki a fait part de l'investissement de principaux acteurs du monde microélectronique (environ 3 G\$) dans l'économie de la vallée de l'Hudson, ou comme certains l'appellent l'"Empire State High-Tech Corridor" autour d'Albany [14]. Au total, ce sont 750 M\$ qui ont été investis à ce jour dans des projets de recherche de la part de l'état et 7.25 G\$ de la part d'institutions privées. 500 personnes hautement qualifiées sont employées dans la vallée et 1000 emplois supplémentaires devraient être créés.

A l'instar de la Silicon Valley, le "High Tech Corridor" suit à son tour le chemin du développement technologique et économique avec la prolifération de laboratoires et de "fabs" pour les nanotechnologies. Alain Kaloyeros, directeur du projet "Nanotechnologie" d'Albany, compare la dynamique de ce pôle de compétitivité à celle d'un centre commercial. Avant d'attirer des acteurs de plus faible envergure (startups), il faut d'abord avoir des partenaires de poids sur place:

<sup>1</sup> MII avait reçu une bourse fédérale de 36 M\$ pour lancer ses activités il y a quelques années et sert d'exemple pour le développement de partenariats dans la région.

un fabricant, IBM (premier centre de R&D créé en 2002), servant de vitrine, un consortium de recherche, Sematech North et un équipementier, Tokyo ELectron (TEL).

ASML est l'un des nouveaux arrivants avec l'établissement de son premier centre de recherche en photolithographie à l'étranger pour un investissement de 325 M\$. Ce projet de recherche s'intitule "International Multiphase Partnership for Lithography Science and Engineering (IMPLSE)". L'arrivée d'ASML à Albany fait de ce lieu un des centres de recherche majeurs en photolithographie au niveau mondial.

Annoncé récemment dans le courant d'un développement des partenariats de recherche mondiaux, le College of Nanoscale Science and Engineering de l'Université d'Albany a fait part de son intention de créer des nouveaux partenariats, par exemple avec l'initiative NanoQuébec menée dans six universités de la province canadienne et avec le CEA LETI en France [15]. Depuis février, l'Université d'Albany a multiplié ses partenariats d'échange avec ses équivalents étrangers au Mexique et en Allemagne notamment avec l'accueil d'étudiants venant de l'Université de Dresde [16] (également pour resserrer les liens entre AMD et Infineon).

S'imposant désormais en contrepoids au géant des composants Intel, ce pôle de compétitivité pourrait rétablir un équilibre technologique entre la côte Ouest, la Silicon Valley et la côte Est.

Aujourd'hui ces trois grands pôles R&D sont en concurrence pour obtenir des financements fédéraux pour la recherche en nanoélectronique. Intel pousse la Silicon valley, Texas Instruments mise sur le Texas et IBM met en avant Albany.

Les autres initiatives nationales de recherche : Devant les investissements majeurs à fournir pour rester compétitifs, les industriels n'ont plus d'autres choix que de se regrouper en consortiums pour unir leurs efforts afin de résoudre des problèmes technologiques majeurs. Parmi les grandes initiatives en Amérique du Nord :

- La Nanoelectronics Research Initiative [17] est une initiative industrielle annoncée par Georges Scalise, président de la Semiconductor Industry Association, en décembre dernier ayant pour but de créer une collaboration accrue des universités, des industries et du gouvernement pour surpasser les principales barrières au développement des semiconducteurs. SIA prévoit un financement sur 15 ans des recherches en nanotechnologies pour arriver à définir des motifs en-dessous des 10 nm.

- SPIE The International Society for Optical Engineering est un organisme à but non lucratif destiné à promouvoir les partenariats scientifiques dans les secteurs de l'optique, de la photonique et de l'imagerie, par le biais de conférences et de publications. SPIE fournit par exemple plus de 700.000\$ par

an de financements pour des bourses et des soutiens financiers à des travaux scientifiques. SPIE comprend une trentaine de groupes techniques chacun traitant d'un sujet en particulier. Bacus est le groupe technique s'occupant du développement de la technologie des photomasques [18]. Créé en 1980, il est aujourd'hui un des rendez-vous incontournables pour les échanges d'informations techniques entre les constructeurs de masques : matériaux, résines, masques à décalage de phase, procédés,...

- Nanoimprint : EVGroup (Autriche) a annoncé en décembre dernier la création d'un consortium de recherche (NILcom) dédié à la commercialisation des techniques de nanoimprint (NIL) [19]. Parmi ses partenaires en Amérique du Nord :

- Moules : Quantiscript Inc. (Québec), Transfer Devices Inc. (Santa Clara)

- Procédés : National Research Council of Canada's Industrial Materials Institute (NRC-IMI)

- Equipement : Applied Microstructures Inc. (San Jose)

# **Technologie**

### 1) Introduction

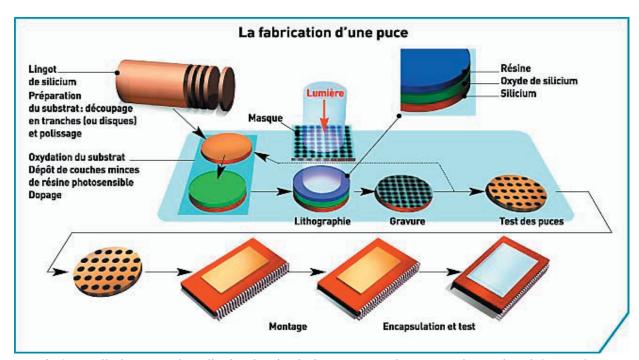

Aujourd'hui une centaine de traitements différents sont nécessaires à la réalisation d'un circuit intégré. L'étape de photolithographie est une étape clé dans le processus de production des composants microélectroniques et s'inscrit dans les procédés de réalisation dit de "Front-end" (Fig.4).

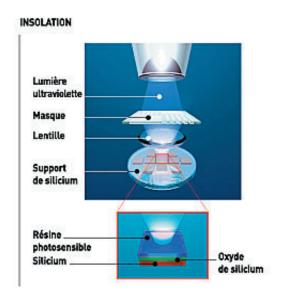

# **Principe de la photolithographie optique** (Fig. 5):

La photolithographie optique est une technique permettant de projeter à l'aide d'une source lumineuse, une image au travers d'un masque, où est définie l'image du circuit, sur une résine photosensible afin de l'y imprimer. Pour la génération actuelle des semi-conducteurs, la source lumineuse est un laser Excimer utilisant un mélange de gaz argon et fluor : il s'agit de la technologie 193 nm (longueur d'onde dans le domaine Deep UV). Ce laser projette l'image du masque, ou réticule, à travers un système d'objectifs avec un taux de réduction allant jusqu'à 1 pour 10. La résine insolée est ensuite éliminée par un révélateur et va aussi servir de masque pour la phase suivante de gravure chimique.

### Relation de Rayleigh:

Le critère de Rayleigh évoque la relation entre la résolution des motifs définis, la longueur d'onde de la source et le pouvoir de résolution de l'appareillage :

### $R=k_1.\lambda/NA$

où R est la résolution du motif (distance minimale visible entre deux objets),  $k_1$  un paramètre dépendant de l'appareillage (résine, masque), NA le pouvoir de résolution de l'appareil (Numerical Aperture) et  $\lambda$  la longueur d'onde de la source.

Fig.4: Détails des étapes de réalisation des circuits intégrés, procédés Front-end et Back-end. Source CEA

| Challenges de la photolithographie                                 |                                                                                                                                                                                                                                                                                               |  |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Dimensions < 50 nm - 2009                                          | Difficultés                                                                                                                                                                                                                                                                                   |  |

| Masques optiques contenant des motifs pour améliorer la résolution | Contrôle des dimensions critiques, taux de défauts dans les masques optiques Développement d'empilements multicouches sans défauts pour les masques Extrême UV Améliorer les techniques d'inspection et de réparation des couches                                                             |  |

| Coût de réalisation et ROI                                         | Amélioration de la productivité des steppers Maîtrise du coût des masques optiques munis de techniques d'amélioration optique (RET) Amélioration de la durée de vie des appareils d'exposition Investissements majeurs pour développer plusieurs technologies simultanément                   |  |

| Contrôle des procédés                                              | Contrôle des dimensions critiques de la grille à moins de 4 nm<br>Amélioration des techniques d'alignement et de superposition<br>indépendemment de la technologie choisie<br>Précision des corrections des effets optiques de proximité<br>Contrôle des effets de flare lors des expositions |  |

| Résines pour la génération 193 nm sèche et par immersion           | Réduction du dégazage lors de l'immersion<br>Réduction des rugosités des lignes<br>Détection et élimination des défauts > 30 nm                                                                                                                                                               |  |

Tableau 5 : Les challenges principaux que doit relever l'industrie sont résumés dans le tableau ci-dessus. Parmi eux, la précision des procédés est un point important à contrôler à des dimensions de 2,2 nm pour la génération 65 nm, les défauts doivent être minimisés pour ne pas induire de déformations dans les motifs définis et le coût global des opérations doit rester minime.

Fig. 5 : Principe de photolithographie optique

La lithographie optique est la technique la plus largement utilisée en production dans les usines microélectroniques depuis une trentaine d'années. Cependant, cette technique doit absolument délivrer de meilleures résolutions, avoir une fiabilité optimum avec des coûts moindres. Ces challenges principaux auxquels l'industrie fait face aujourd'hui sont regroupés dans le Tableau 5. Alors que la technologie à 193

nm est bien assimilée actuellement, il faudra développer de nouvelles techniques d'augmentation de la résolution ou RET (Resolution Enhancement Technique) pour améliorer l'image du masque dans la résine. Les sources émettent en effet aujourd'hui à des doses faibles ce qui induit des problèmes de contraste pour définir des motifs dans la résine.

#### 2) Les procédés de la NGL

# a) Lithographie 193 nm par immersion

La lithographie par immersion est apparue pour la première fois dans les sessions du salon sur la Microlithographie tenu en 2002 à San Jose (CA). Cette solution technologique pour succéder aux techniques optiques dites "sèches", a connu un succès fulgurant en quelques années et est maintenant développée par les plus grands constructeurs. Un de ses avantages majeurs est qu'elle ne nécessite pas un changement important de l'infrastructure lithographique des salles blanches.

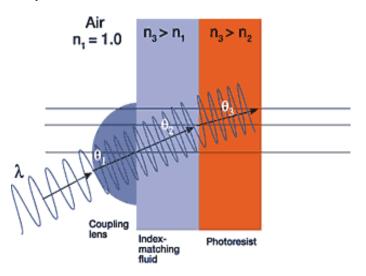

<u>Principe</u>: La technique de lithographie par immersion se base sur la présence d'un liquide entre les derniers éléments optiques du stepper, d'où provient la lumière de la source, et la plaquette de silicium à définir. Le liquide possède un indice de réfraction supérieur à l'air ( $n_{eau} = 1,44 > n_{air} = 1$ ), ce qui réduit la longueur d'onde effective de la lumière incidente et ainsi améliore la résolution selon la relation de Rayleigh.

Sur la Fig. 6, le front d'onde passe du milieu air (n=1) à travers une lentille sphérique n<sub>3</sub>, le fluide d'immersion n<sub>2</sub> puis la résine photosensible n<sub>1</sub>. La longueur d'onde effective est obtenue en divisant la longueur d'onde totale par l'indice de réfraction du milieu : pour un stepper à 193 nm, il est possible d'obtenir des longueurs d'onde effectives de 134 nm après passage à travers le liquide.

Fig.6 : Le front d'onde incident traverse des milieux (lentille, fluide, résine) d'indices de réfraction différents, réduisant sa longueur d'onde effective et améliorant la résolution.

Plusieurs configurations sont envisagées pour introduire l'eau dans le système :

- design "douche" dans lequel l'eau est déposée sur la plaquette puis vidée à chaque insolation (ce design est actuellement privilégié par les grands constructeurs comme Nikon et ASML);

- design "baignoire" dans lequel la plaquette baigne dans le liquide et se déplace suivant les différentes étapes du procédé;

- design "piscine" où le système tout entier baigne dans le liquide.

Amphibian Systems Inc., une start up issue du Rochester Institute of Technology RIT (NY), a vendu cette année son premier microstepper par immersion "Amphibian XIS" pour des applications R&D des technologies de 90 à 30 nm [20]. L'appareil existe avec une double source d'exposition (248 nm ou 193 nm), des designs de lentilles avec des pouvoirs de résolution de 0,54 à 1,6 et peut accueillir des plaquettes de 150 à 300 mm. Le RIT a démontré lors du salon Microlithography 2005 qu'il était possible de définir des lignes et des espaces de 31 nm avec la technologie par immersion [21], un composé de phosphate d'hydrogène comme fluide et des lentilles de quartz de 1,54 NA. Les chercheurs vont utiliser des optiques en saphir avant un indice de réfraction de 1,93 pour améliorer les résolutions et atteindre 28 nm. IBM, qui a installé dans son centre de R&D 300 mm d'Albany à East Fishkill (College for Nanoscale Science and Engineering) un appareil lithographique à immersion Twinscan AT:1150i de chez ASML, a réalisé en début d'année des prototypes de processeur PowerPC 64 bits par cette technique. Les ingénieurs voulaient démontrer la faisabilité de cette technologie en production : logistique des plaquettes, alignement, dépôt des résines, ... avec des seuils comparables aux appareils de lithographie sèche.

Même si la technique obtient de bons résultats dans les laboratoires, certains sont sceptiques quant à la réussite en production et indiquent que l'immersion n'ira pas au delà de la génération 45 nm, à cause des limitations induites par l'indice de réfraction de l'eau et de l'ouverture numérique des lentilles difficile à maximiser. En effet, une des grandes questions qui subsiste est de savoir si l'un des trois grands constructeurs, ASML, Canon ou Nikon, pourra délivrer un appareil fonctionnant à temps pour la production, optimisé technologiquement mais aussi économiquement. Intel reste encore discret sur l'utilisation de l'immersion en photolithographie pour la génération 65 nm et préfèrerait étendre la durée de vie de sa technologie sèche jusqu'à 45 nm puis enchaîner directement avec les techniques Extrême UV. La politique d'AMD est différente, car elle envisagerait plus une utilisation immédiate de la lithographie par immersion et ceci sur un long terme si les résultats sont concluants.

## b) Technologie 157 nm

Devant succéder à la technique de lithographie sèche à 193 nm, la lithographie à 157 nm est mise de côté aujourd'hui à cause de nombreux problèmes techniques, notamment des résines, retardant sa mise en place. Les coûts de transition vers une telle technologie sont également mis en avant pour expliquer son abandon, par rapport à des techniques comme la lithographie à 193 nm par immersion beaucoup moins chère et plus avancée en terme de prototypage. Certains organismes de R&D développent toujours cependant ce procédé qui pourrait être introduit avec une technique d'immersion pour les futures générations technologiques. Le consortium japonais Semiconductor Leading Edge Technologies Inc. présentait notamment en mars dernier des lignes de 32 nm définies avec une technologie 157 nm par immersion [22] avec des optiques d'ouverture numérique 1,47 en indiquant qu'il s'agissait d'un appareil bêta et qu'il restait encore beaucoup d'améliorations à faire. Un autre groupe des Lincoln Laboratories du MIT [23] a développé des scanners 157 nm par immersion avec une ouverture numérique de 1,7 mais indiquait par ailleurs que l'imagerie optique pour l'inspection des plaquettes restait un problème pour cette longueur d'onde.

### c) Extrême UV (EUV)

L'Extrême UV est étudié depuis de nombreuses années dans les laboratoires de R&D à travers le monde et est soutenu par des géants des semiconducteurs comme Intel pour succéder aux générations optiques du DeepUV. Une incertitude demeure cependant sur son avenir avec une question de fond : cette technologie est-elle viable en production ? Même si Intel continue de pousser son développement pour la génération 45 ou 32 nm (2010 et

2013), beaucoup de problèmes demeurent. Malgré les progrès réalisés pour obtenir des sources plus puissantes, les résultats actuels sont toujours insuffisants : de 25 à 30 W (les requis sont de 100 W par source). Les résines ont des problèmes de sensibilité à cause des faibles doses des sources.

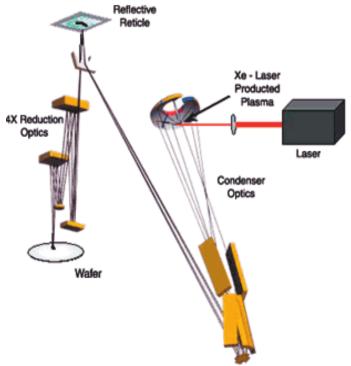

Le rayonnement Extrême UV fait partie de la gamme des X-mous, soit une longueur d'onde de 13,5 nm. A la différence des longueurs d'onde utilisées actuellement (193 nm), le rayonnement EUV est absorbé par la matière : air, verre,... Il faut donc utiliser des masques en réflexion à la difference des masques en transmission actuels et faire fonctionner le tout sous vide (Fig.7). Le contrôle des procédés doit être extrêmement précis pour avoir une efficacité maximale et éviter toute contamination, lors de la manipulation des masques notamment.

Fig.7 : Principe de fonctionnement de la technique EUV. La différence principale avec les autres techniques optiques est la nécessité de travailler sous vide avec un masque en réflexion. Source : Future Fabs

Au niveau des recherches académiques, l'année dernière, l'Université de Central Florida s'est dotée d'un nouveau centre de recherche sur la technologie EUV [24]. La compagnie californienne Northrop Grunman finance le projet à la hauteur de 22 M\$ et fournit les équipements et les droits de propriété intellectuelle. L'équipe du College of Optics and Photonics travaille à l'élaboration de plasmas pour les sources EUV.

Beaucoup sont sceptiques sur les débouchés de cette technologie: Grant Wilson de Molecular Imprint Inc. indiquait lors de la conférence SPIE Microlithography 2005 que "personne ne réaliserait une plaquette avec profit grâce à cette technologie". Le Dr Fabian Pease [25] de l'Université de Stanford y a rappelé aussi l'abandon des techniques de lithographie par rayons X après des investissements de plusieurs G\$ dans les années 70 et 80. D'autres

sont plus optimistes : Christophe Ober de l'Université de Cornell mise sur le développement d'un nouveau type de résines moléculaires pour améliorer les sensibilités actuelles. Intel a annoncé également la commercialisation toute proche de sa technologie avec un coût comparable à la technologie par immersion et des lentilles à très fort pouvoir de résolution (hyper NA) soit de 25 à 30 M\$.

#### d) Nanoimprint

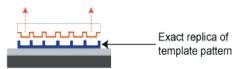

La technique de Nanoimprint est une technique récente (elle a été introduite dans les tables de l'ITRS en 2003) et alternative aux technologies optiques actuelles. Dans ce procédé, les composants sont imprimés de manière séquentielle (Fig.8). Un moule tridimensionnel ou "template" (défini par un faisceau électronique sur un substrat SiO<sub>2</sub>) dont la température est élevée au-dessus de la température de transition du verre est appliqué contre une résine, qui est ensuite solidifiée par une exposition UV. Le moule est ensuite refroidi puis déplacé à un autre endroit pour reproduire ce même processus.

Step 1: Orient template and substrate

Step 2: Dispense drops of liquid imprint resist

Step 3: Lower template and fill pattern

Step 4: Polymerize imprint fluid with UV exposure

Step 5: Separate template from substrate

Fig.8 : Technologie SFIL de Nanoimprint développé par Molecular Imprint Inc.

La technique de lithographie Nanoimprint Step and Flash Imprint (SFIL) a été élaborée dans les laboratoires de l'Université d'Austin au Texas. A la différence des techniques de photolithographie classiques, le Nanoimprint ne requiert aucun équipement optique coûteux, ni de source élaborée ou de résines spécifiques, et fonctionne de plus à des faibles pressions et températures voisines de l'ambiante.

Molecular Imprints Inc., en collaboration avec KLA Tencor, Motorola, Photronics et l'Université du Texas à Austin, ont créé un projet de recherche commun sur 3 ans pour développer la technologie de Nanoimprint, le tout supervisé par le NIST dans son projet de Advanced Technology Program (17M\$) [26]. Ce projet vise à démontrer la faisabilité de la technique au niveau des dimensions imprimables, alignement, superposition, mais aussi en terme de productivité. S'il réussit à optimiser ces critères, ce projet permettrait de rétablir la suprématie américaine dans le domaine des équipements photolithographiques.

L'approche nanoimprint de Nanonex Inc. [27] (Princeton, NY) consiste à utiliser une double couche dans laquelle la couche supérieure polymère est imprimée par un moule. Le motif est ensuite fixé par une exposition ultraviolette et les surfaces amincies sont enlevées par gravure ionique. La résine ainsi formée sert de masque pour la gravure de la couche sousjacente. Ce procédé se passe également à faible temperature et faible pression.

Lors de la conférence Microlithography 2005, les constructeurs de matériels Nanoimprint ont souligné l'intérêt de cette technologie en montrant les améliorations obtenues : meilleure productivité, meilleur alignement, meilleure résolution (moins de 10 nm) et pour des prix moindres comparés aux scanners optiques : 100.000 \$ pour un appareil lithographique de Nanoimprint contre de 18 à 25 M\$ pour les scanners optiques à 193 nm. Molecular Imprints Inc. présentait un nouveau modèle destiné aux futures générations de composants : le i300. La compagnie a entamé sa transition d'applications de niche vers la production de masse. Nanonex présentait une machine capable de garantir la faisabilité de la génération 10 nm grâce à une technologie de Air Cushion Press (ACP) pour garantir une meilleure uniformité sur toute la surface de la plaquette ainsi qu'une meilleure précision. HP, avec la machine fournie par le constructeur allemand Suss Microtec AG, a créé un réseau de mémoires moléculaires à 65 nm.

Alors que les constructeurs encensaient leur technique, les analystes sont restés plus circonspects sur le devenir de la technologie soulignant la fragilité du marché encore naissant. Pour l'instant, la plupart des appareils vendus l'ont été pour des laboratoires de biotechnologies, MEMS,... Les prévisions de ventes pour 2005 sont de 45 à 60 appareils, mieux que les 40 appareils vendus en 2004 affirme Ken Mason, président de Encrease Inc. (Hampstead, NH) une compagnie de marketing représentant le constructeur suédois Obducat spécialisé dans l'équipement pour Nanoimprint.

# e) Dip Pen Nanolithography (DPN)

La technique de Dip Pen Nanolithography est une technique d'écriture directe qui définit des motifs sur un substrat en déposant les molécules avec la pointe d'un microscope à force atomique (AFM). Les molécules se fixent par chemisorption ou interactions électrostatiques sur la surface.

Quand des chaînes alcanethiols sont déposées sur une surface d'or, une monocouche se forme où les groupements thiols forment des fortes liaisons avec l'or et les chaînes d'alcane s'étendent quasiment perpendiculairement à la surface.

L'avantage de cette technique est qu'elle ne nécessite pas l'utilisation de résines et ainsi des motifs avec des tailles caractéristiques de 15 nm peuvent être réalisés. Un autre atout de la technique est sa capacité à imager et à écrire un motif avec le même dispositif, plusieurs encres pouvant être déposées sur un même substrat avec un très bon alignement. Pour passer à la production, ces pointes miniatures peuvent être disposées en réseau afin d'augmenter le rendement des structures créées. Aujourd'hui des réseaux de 1.3 millions de pointes existent.

Nanoink Inc., basé à Chicago et créé par Chad Mirkin du Northwestern University Nanotechnology Institute, commence à commercialiser des appareils de lithographie à base de la technique de DPN [28]. Aujourd'hui les brevets délivrés concernant la technique de DPN sont au nombre de 3 aux USA et 6 dans le monde. Nanoink détient l'exclusivité des droits de propriétés intellectuelles. En 2003, Nanoink et Carbon Nanotechnologies Inc. signaient un accord de collaboration sur le DPN pour développer des techniques de dépôt de nanotubes de carbone [29].

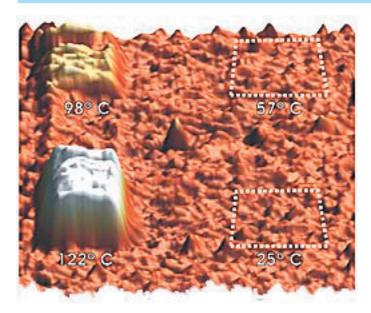

Une équipe de recherche de GeorgiaTech et des Naval Research Laboratory (NRL) (Surface Nanoscience and Sensor Technology Section) ont développé une nouvelle technique de Thermal DPN (Fig.9) incluant un module de chauffage à la pointe d'un microscope AFM permettant de réguler le flux d'encre [30].

L'utilisation d'une encre solide permet également de définir des motifs dans le vide sans que l'encre ne s'évapore. Les chercheurs ont utilisé une encre à base d'acide phosphonique (OPA), fondant à 100°C. Cette technique permet de détecter la rugosité en surface et de déposer l'encre aux endroits souhaités. La recherche a été financée par la National Science Foundation (NSF), Office of Naval Research (ONR) et l'Air Force Office of Scientific Research (AFOSR).

Fig. 9 : Technique de DPN thermique développée par l'Université de Georgia Tech. Suivant les températures de la pointe, le flux d'encre est régulé : à 122°C, le matériau est déposé sur la surface du substrat, alors qu'à 25 et 57°C, le phénomène est bloqué. Source : GeorgiaTech

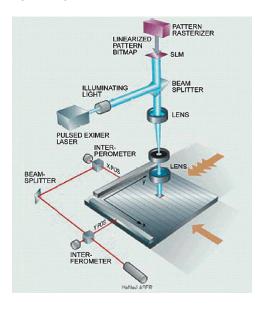

## f) Lithographie sans masque (ML2)

Lors du Maskless Meeting organisé par Sematech et tenu à San Jose en Janvier dernier, de nombreuses entreprises et équipes universitaires ont présenté des techniques de lithographie sans masque différentes, restant toutefois à l'état embryonnaire [31]. Cette technologie ML2 reste toutefois en développement à cause de capacités de production lentes, une complexité inhérente à la technique et des niches incertaines qui mettent en attente son introduction en 2007 pour la génération 45 nm. Parmi les participants à cette conférence, ST Microelectronics a annoncé qu'il avait déjà un prototype d'écriture directe pour son flux de production interne. Les ingénieurs de ST ont souligné que cette technique permet de réaliser des "produits sélectionnés" (cellule SRAM à 6 transistors de 0,25 micron²) et est destinée à la fabrication de circuits à applications spécifiques pour de faibles volumes et donc plutôt des applications de niches qu'en remplacement des procédés dominants. Un des paramètres à améliorer sera la productivité : l'objectif à long terme est de passer la barre des 50 plaquettes par heure alors que la photolithographie optique atteint des niveaux de 120 plaquettes par heure actuellement.

Il existe deux approches différentes pour la lithographie sans masque : l'optique (OML2) (Fig.10) et l'impulsion chargée (CPML2). Aujourd'hui les entreprises japonaises sont parmi les plus avancées dans ces deux domaines. La compagnie suédoise Micronic Laser Systems AB fait partie des développeurs les plus actifs de la technique optique et a annoncé récemment l'envoi d'une machine test chez un grand constructeur microélectronique. Aux Etats-Unis, le laboratoire Lawrence Livermore (LLNL)

avec l'Université de Stanford effectuent des recherches sur la lithographie sans masque à particules chargées (CPML) : au LLNL, le projet de recherche se base sur l'utilisation de d'électrodes électrostatiques pour envoyer et accélèrer les faisceaux d'ions dans une machine à 75 KeV, une technique dite de lithographie à réduction de micro-faisceaux sans masques (MMRL).

Fig. 10 : Principe de lithographie sans masque optique. La technique utilise le support classique de la photolithographie optique à la différence que le photomasque est remplacé par un réseau de modulateurs lumineux contrôlant l'image définie.

Cependant, contrairement au Japon et à l'Europe, le secteur du ML2 aux Etats-Unis est en pleine confusion. Les sociétés américaines ont eu une désagréable surprise lors du séminaire sur la lithographie sans masque où la DARPA a annoncé ne plus souhaiter financer cette technologie émergente aux Etats-Unis. Ce revers pourrait anéantir les tentatives américaines dans ce domaine, dont un grand nombre a été présenté lors du séminaire sur la technologie sans masque. Avec une nouvelle approche sur ce problème, la jeune entreprise américaine, Multibeam Systems Inc. (Santa Clara, CA) est la dernière société à être entrée sur ce marché émergeant. Multibeam Systems (MS) vise à développer un réseau de 10 colonnes de faisceaux électroniques pouvant écrire une plaquette entière de silicium en un seul passage avec une vitesse 100 fois supérieure aux techniques actuelles. MS utiliserait des faisceaux électroniques de forte énergie avec des formes carrées pour éviter les problèmes de définition en bord de faisceaux.

Une autre jeune entreprise américaine, Novelx Inc. (Lafayette, CA), a annoncé une technologie à module monolithique pour l'utilisation d'une lithographie sans masque à faisceaux d'électrons. Le pionnier en matière de lithographie sans masque, Emission Systems Inc. (Wellesley Hills, Massachusetts) rebaptisé Arradiance Inc., a rassemblé des fonds et a progressé dans sa technologie à faisceaux

multiples. IBM travaille au développement d'une technologie hybride combinant e-beam et scanner optique destiné à la production d'ASIC et de circuits intégrés à faible volume. Ainsi des lignes de 30 nm ont pu définies avec un appareil à faisceau d'électrons VB6:HR de chez Leica Microsystems.

Les risques encore très forts qui gravitent autour de cette technique effraient les capitaux risqueurs qui voudraient voir un prototype en fonctionnement avant d'investir plus massivement vers une commercialisation des procédés.

## g) Auto-assemblage

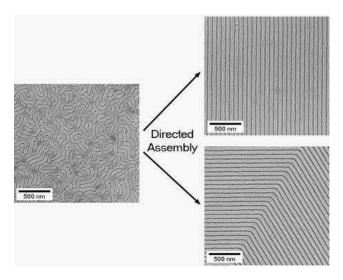

Les difficultés de l'assemblage de la matière à l'échelle atomique viennent des effets quantiques, de variations statistiques des propriétés et des effets de surface. La solution idéale pour la lithographie future des composants électroniques à l'échelle du nanomètre serait qu'ils puissent s'auto-assembler selon des structures prédéfinies. Ce sujet est pleinement d'actualité aux Etats-Unis et de nombreuses équipes travaillent dans ce sens. Par exemple, une équipe internationale de chercheurs de Wisconsin, Madison, du Korea Advanced Institute of Science and Technology et du Paul Scherrer Institute en Suisse ont créé une méthode hybride pour définir des motifs en silicium à partir d'un mélange de polymères (Fig.11).

Figure 11: A gauche, la mixture copolymères à blocs désordonnée. A droite, les chercheurs ont réussi à arranger le mélange de manière uniforme pour former des structures. La recherche a été effectuée au Center for Nanotechnology de l'Université de Madison. Elle a été financée par la Semiconductor Research Corporation et la National Science Foundation's Nanoscale Science and Engineering Center.

Ce mélange consiste en une association de copolymères à blocs et de deux de ses constituants, les homopolymères : 60% en masse volumique de polystyrène-block-poly(méthylméthacryl ate), 20% polystyrène et 20% poly(méthylméthacrylate). Les chercheurs ont montré qu'en appliquant cette substance sur un substrat silicium recouvert d'une couche de polystyrène

préalablement gravée chimiquement à l'échelle nanométrique, il était possible de créer des motifs réguliers, localisés et de formes différentes grâce à la redistribution locale du mélange des homopolymères sur la surface. La gravure chimique a pour effet de rendre les régions gravées hydrophiles. La composante polymère du mélange adhère préférentiellement aux régions non gravées alors que le poly(méthylméthacrylate) comble les régions chimiquement modifiées. Un recuit permet ensuite de stabiliser les structures prédéfinies.

Par ailleurs, la NSF finance de nombreux projets sur les méthodes de nanofabrication (Projet Nanomanufacturing) :

- Nanoscale Interdisciplinary Research Teams (NIRT): programme de recherche et d'éducation interdisciplinaire notamment pour le nanomanufacturing de cristaux photoniques à large bande interdite. Université de Boulder au Colorado en partenariat avec Agilent Technologies montant :1,115,000 \$

- John Hopkins University (Maryland) : programme de recherche et d'éducation sur l'auto-assemblage de structures grâce à la tension de surface dans les fluides (400,000\$). Projet CAREER

- Université d'Urbana Champaign (IL) sur l'autocroissance des nanotubes de carbone (fin 2005)

#### Conclusion

L'industrie des semiconducteurs n'a cessé de chercher à repousser les limites d'utilisation des techniques optiques pour minimiser les coûts de production. Dans les années à venir, ces techniques devraient continuer à être utilisées massivement grâce au développement de la lithographie par immersion à 193 nm et ainsi permettre une transition aisée vers une nouvelle génération lithographique. A plus long terme, l'Extrême UV et le Nanoimprint sont les techniques les plus prometteuses développées par les grands acteurs du secteur microélectronique. Des prototypes fonctionnant avec des seuils de productivité corrects sont cependant toujours attendus et il n'est pas garanti que ces techniques puissent être adaptées aux modes de production massive d'un point de vue technologique et économique. D'autres solutions comme la lithographie sans masque seraient intéressantes au niveau économique puisqu'elle permet de faire l'économie du coût des masques mais ne sont pour l'instant destinées qu'à des applications de faible volume. Le facteur financier sera primordial dans le choix des futures techniques de photolithographie et les entreprises devront continuer leurs efforts de recherche communs par le biais de consortium, comme l'ITRS, et de clusters technologiques, telle la vallée de l'Hudson à New-York, pour commercialiser la Nouvelle Génération Lithographique.

> Michaël Nique, Mission pour la Science et la Technologie, San Francisco.

### Références

- [1] Rapport annuel de la Semiconductor Industry Association : http://www.sia-online.org/downloads/SIA\_AR\_2005.pdf

- [2]International Roadmap for Semiconductors: http://public.itrs.net/Files/2003ITRS/Home2003.htm

- [3] Grands challenges techniques pour 2006 définies par Sematech : http://www.sematech.org/corporate/news/releases/20050418.htm

- [4] Montgomery Research Inc: http://www.future-fab.com/documents.asp?grID=208&d\_ID=3002

- [6] Partenariat IMEC et ASML sur l'Extreme UV : http://www.imec.be/wwwinter/mediacenter/en/EUV\_2004.shtml

- [7] Applied annonce son souhait de créer une holding de sq compagnie en Chine à Xian : http://www.appliedmaterials.com/news/pr2005.html?menuID=6

- [8] Une vingtaine d'usines de production de composants devraient voir le jour sous peu en Chine : http://wps2a.semi.org/wps/portal/\_pagr/117/\_pa.117/122?dFormat=application/msword&docName=P035692

- [9] Texas Technology Initiative créé en 2004 par le gouverneur du Texas : http://www.texasnano.org/

- $[10] \ Initiative \ Emerging \ Technology \ Fund \ pour \ relancer \ l'emploi \ au \ Texas : http://www.texasnano.org/pdfs/Emerging\%20 \ OTechnology\%20 \ Fund\%20 \ White\%20 \ Paper.pdf$

- [11] Advanced Materials Research Center à l'Université du Texas à Austin : http://www.mrc.utexas.edu/amrc/

- [12] Alliance technologique SPRING au Texas: http://www.cnm.utexas.edu/partnerships spring.htm

- [13] Discours du State of the State Address prononcé par Georges Pataki le 5 janvier 2005 : http://www.state.ny.us/sos2005/05sos media downloadb.html

- [14] Pôle de compétitivité new-yorkais installé à Albany : http://www.albanynanotech.org/news/index.cfm

- [15] Partenariat Albany, Cea Leti et NanoQuebec : http://www.albanynanotech.org/news/index.cfm?step=show\_detail&NewsID=277

- [16] Echange d'étudiants entre l'Université de Dresde en Allemagne et Albany : http://www.albanynanotech.org/news/index.cfm?step=show detail&NewsID=274

- [17] Nanoelectronics Research Initiative lancé par SIA: http://www.sia-online.org/pre\_release.cfm?ID=343

- [18] Groupe technique sur les photomasques créé par SPIE : http://www.spie.org/Membership/index.cfm?fuseaction=TG\_BACUS\_scholarship

- [19] Consortium industriel sur la R&D en nanoimprint : http://www.nilcom.org/

- [20] Amphibian Systems Inc. a vendu son premier microstepper à immersion : http://www.eetimes.com/news/semi/show Article.jhtml?articleID=60404564

- [21] Le Rochester Institute of Technology a réussi à définir des lignes de 31 nm avec une technique d'immersion : http://www.eetimes.com/news/semi/showArticle.jhtml?articleID=60403852

- [22] Technologie 157 nm: http://www.eetimes.com/news/semi/showArticle.jhtml?articleID=60405628

- [23] Lincoln Laboratory du MIT : http://www.ll.mit.edu/

- [24] L'University of Central Florida se dote d'un centre sur la recherche EUV : http://www.irconnect.com/noc/press/pages/news releases.mhtml?d=62472

- [25] Page de présentation du Dr Fabian Pease de l'Université de Stanford : http://chomsky.stanford.edu/~pease/

- [26] Projet nanoimprint financé par le NIST: http://www.molecularimprints.com/AboutMII/NIST.html

- [27] Approche technologique de Nanonex Inc. sur le nanoimprint : http://www.nanonex.com/Technology.htm

- [28] Technique de Dip Pen Lithography développé par Nanoink Inc : http://www.nanoink.net/4200\_dpn.html

- [29] Nanoink et Carbon Tchnologies s'associent pour développer la technique DPN : http://www.cnanotech.com/pages/resources and news/press release archive/press story NanoInk.html

- [30] Technique de DPN thermique développée par une équipe de Georgia Tech : http://gtresearchnews.gatech.edu/newsrelease/tdpn.htm

- [31] Conférence Maskless Meeting organisé par Sematech : http://www.sematech.org/corporate/news/releases/20050120b.htm

# ETATS-UNIS SCIENCES PHYSIQUES

NANOSCIENCES, MICROELECTRONIQUE, MATERIAUX

N°21, Juillet-Août 2005

Pour vous abonner gratuitement à la lettre ETATS-UNIS SCIENCES PHYSIQUES et être informé en priorité de la disponibilité des prochains numéros, il suffit d'envoyer un courrier électronique à l'adresse: subscribe.physiques.usa@adit.fr

Vous recevrez en retour une confirmation d'abonnement.

Directeur de la publication : Michel ISRAEL

Rédacteurs en chef : Roland HERINO Christophe LEROUGE

Rédacteurs : Michael Ronan NIQUE

Mise en page et Publication : Michael Ronan NIQUE

ETATS-UNIS SCIENCES PHYSIQUES est une publication mensuelle (dossier trimestriel) de la Mission pour la Science et la Technologie de l'Ambassade de France aux Etats-Unis, dont le site internet est: http://www.france-science.org

Vous y trouverez un archivage des anciens numéros de la lettre et découvrirez aussi les autres publications de la Mission pour la Science et la Technologie

- -S&T Presse

- -Flash TIC

- -Revue santé Etats-Unis

- -Revue de l'environnement

- -Etats-Unis Espace

- -Etats-Unis Microélectronique/ Matériaux (archives précédant la fusion)

#### Les publications de la Mission pour la Science et la Technologie:

Vous pouvez également lire nos fiches stratégiques, dossiers et rapports d'études suivants sur le site de la Mission pour la Science et la Technologie www.france-science.org

### FICHES STRATÉGIQUES:

- Bio-Pharming Des plantes génétiquement modifiées pour produire des médicaments, (Jan 2005)

- Comment fonctionnent les universités américaines ? (Jan 2005)

- L'environnement au sortir des élections américaines : bilan et perspectives, (Jan 2005)

- Nanoélectronique USA, (Jan 2005)

- Préserver l'eau dans l'agriculture texane : contexte et solutions, (Jan 2005)

- SpaceShipOne : le début ou la fin du rêve ? (Jan 2005)Bio IT

- USA (Juin 2004)

- Conséquences sur les scientifiques de la politique des visas d'entrée aux Etats-Unis (Juin 2004)

- Galileo/GPS, une nouvelle forme de partenariat transatlantique (Juin 2004)

- La National Science Foundation (Juin 2004)

- La place des universités dans le système de R&D aux Etats-Unis (Juin 2004)

- La proposition de budget 2005 du président américain pour les les « National Institutes of Health » (Juin 2004)

- La proposition de budget 2005 du président Bush pour les « Centers for Disease Control and Prevention (CDC) » Juin (2004)

### DOSSIERS ETATS-UNIS SCIENCES PHYSIQUES:

- Février 2005 : L'électronique grand public aux Etats-Unis

- Juillet 2004: L'International Roadmap for Semiconductors

- Mai 2004 : Les nanocomposites aux Etats-Unis

- Octobre 2003 : Le stockage des données

#### NOTES ET RAPPORTS D'ETUDES:

- Mar 2005 : La spintronique aux Etats-Unis Un Aperçu des Recherches

- Fev 2005 : Eau et agriculture au Texas

- Oct 2004 : Fonctionnement des universités américaines : Qui Propose ? Qui décide ?

- Sep 2004 : Nouvelles Modalités d'attribution des visas aux US, quelle influence sur la communauté scientifique?

- Jul 2004 : Les Universités Américaines: Quelques données

- Jul 2004 : Quelles sont les forces qui entraînent la R&D américaine ?

- Juin 2004 : Analyse du secteur biotechnologies animales aux Etats-Unis en 2003

- Avr 2004 : Le statut des chercheurs aux Etats-Unis

- Avr 2004 : Les projets de création de laboratoires à la NSF

- Mar | 2004 : La National Science Foundation

- Fev 2004 : Un aperçu des technologies dans la Silicon Valley Tendances et Perspectives

- Fev 2004 : R&D Industries 2004

- Fev 2004 : La Bioinformatique en Californie

- Dec 2003 : R&D 2004, Un budget à deux vitesses